基于FPGA的脉冲参数测量仪的设计(论文18000字)

摘要:在现代战争中,电子侦察起到越来越重要的作用,而它的前提和基础便是快速、高精度的脉冲参数测量,因此设计出速度快且精度高的脉冲参数测量仪在实际应用中具有非常重要的意义。本设计以FPGA为载体,基于SOPC技术,运用等精度测量原理,以外围信号调理电路与内部嵌入软核处理器的FPGA相结合的方式,实现了对频率、周期、幅度、脉宽、占空比及上升沿上升时间等脉冲参数的高精度测量,达到了系统高精度的要求。

系统中前期硬件电路模块为脉冲信号的各个参数的信号调理电路,它们负责对输入的脉冲信号进行放大和整形等处理。本设计采用一块飓风四代FPGA芯片EP4CE15F17C8N作为测量平台和系统控制中心,在Quartus II开发环境中以VHDL语言编写计数器等逻辑功能模块的具体计数逻辑,同时在Nios II IDE软件中用C语言编写软核Nios II的应用程序,运用了FPGA高速并行的特点完成对脉冲各参数的高速采集。计数器功能模块负责计数,软核Nios II则负责信号控制、数据计算处理和驱动液晶屏显示等,二者相互协调,实现了FPGA和嵌入式微处理器的无缝结合,从而缩短了开发周期,提高了系统可靠性,降低了开发成本。

设计全过程都在文中得到了说明,重点介绍了本系统等精度测量原理、测量方案的制定、外围硬件电路的设计、FPGA内部逻辑功能模块的设计和FPGA内嵌的软核处理器编程设计等内容,介绍的同时还给出了相应的图表进行辅助说明。文章记录下了本系统在整体实物测试时的测量结果,并以表格形式呈现,测量数据表明本设计精度高、误差率低、稳定性好。

关键词:现场可编程逻辑门阵列;脉冲参数;可编程片上系统;NiosII;等精度

Design of Pulse Parameters Measurement Instrument based on FPGA

Abstract:In modern wars, electronic reconnaissance becomes more and more important, and the pulse parameters measurement with fast speed and high precision is its premise and basis, so the design of high speed and high precision pulse parameters measurement instrument is very important in practical applications. This design uses FPGA as the carrier, based on SOPC technology, using the principle of equal precision measurement, in combination of external signal modulate circuits and FPGA with embedded processor, and realizes the high precision measurement of frequency, cycle, amplitude, pulse width, duty ratio and pulse rise time parameters, so it reaches the high-precision system requirements.

The hardware circuits of the system are the signal modulate circuits, which is responsible for amplification and reshaping of the input pulse signals. This design uses a hurricane fourth generation FPGA chip EP4CE15F17C8N as the measuring platform and system control center, programming specific logic codes of counters with VHDL language in Quartus II development environments, writing application programs of soft-core with C language in the Nios II IDE software, and realizes high-speed acquisition to pulse parameters with the high-speed and parallel processing characteristics. Counters are responsible for counting, soft-core Nios II is responsible for controlling signals, calculating and processing data and driving liquid crystal display, the two interact with each other coordinately to achieve a seamless integration of FPGA and the embedded microprocessor, so as to shorten the development cycle, improve system reliability and reduce the costs of development.

This paper introduces the whole process of the design, and lays special stress on introducing principle of the measurement, establishment of the measurement plan, design of the hardware circuits, design of internal logic function modules of FPGA and programming design of the embedded processor, the paper also provides corresponding charts for auxiliary descriptions. In this paper, the measurement results of the system in testing phases are recorded and presented in the form of tabular. The measured data show that the design has high accuracy, low error rate and good stability.

Key words:FPGA; pulse parameters; SOPC; NiosII; equal precision measurement

目 录

1 绪论 1

1.1研究目的及意义 1

1.2国内外研究现状 1

1.3 本文主要研究内容 2

2 系统载体FPGA开发介绍 3

2.1 FPGA基本结构及开发语言 3

2.2 FPGA器件分类及编程下载 4

2.3系统开发环境简介 4

2.3.1 QuartusII软件简介 4

2.3.2 NiosII IDE软件简介 5

2.4本章小结 5

3 等精度脉冲参数测量原理 5

3.1脉冲信号及参数定义 5

3.2脉冲参数测量系统结构框图 6

3.3频率测量方法 7

3.3.1传统测量方法简介 7

3.3.2等精度测频法 7

3.4占空比测量方法 9

3.4.1传统测量方法简介 9

3.4.2等精度测量法 9

3.5上升时间测量方法 10

3.5.1传统测量方法简介 10

3.5.2等精度测量法 10

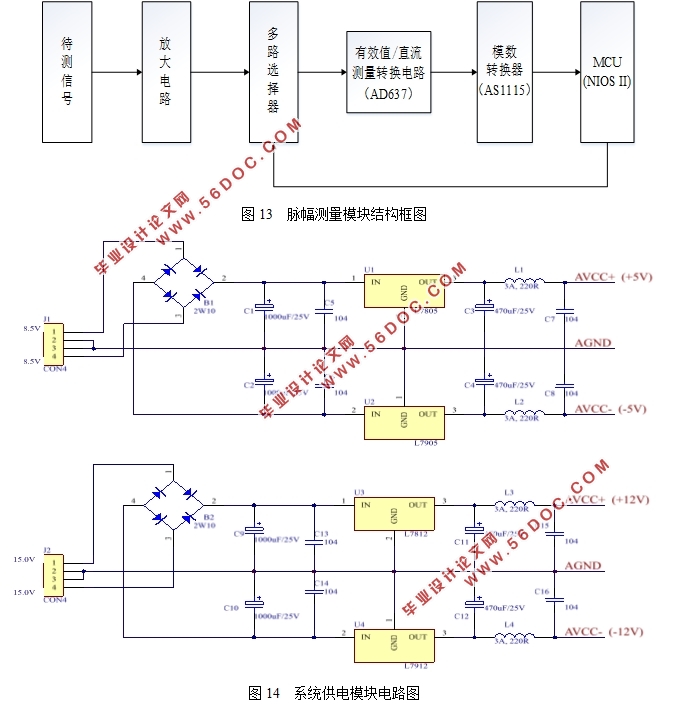

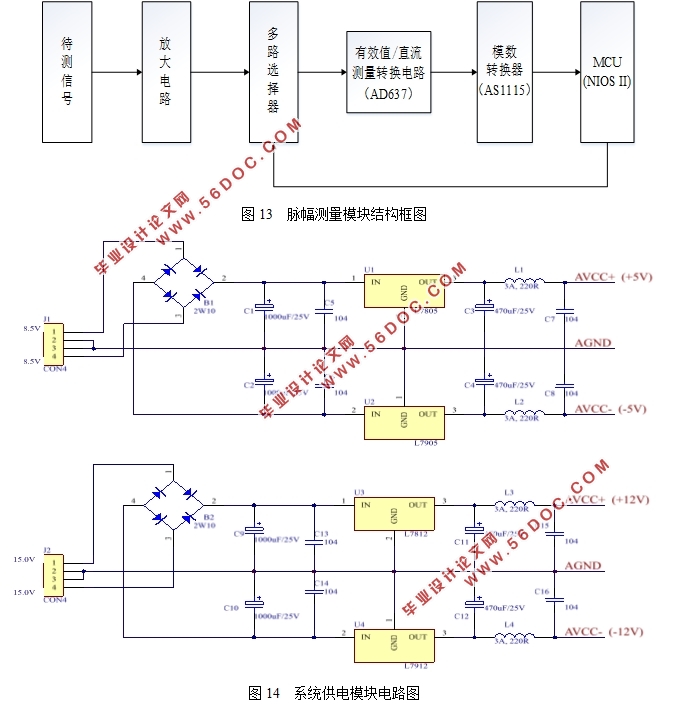

3.6脉冲幅度测量方法 11

3.7本章小结 12

4 外围硬件模块及FPGA系统设计 12

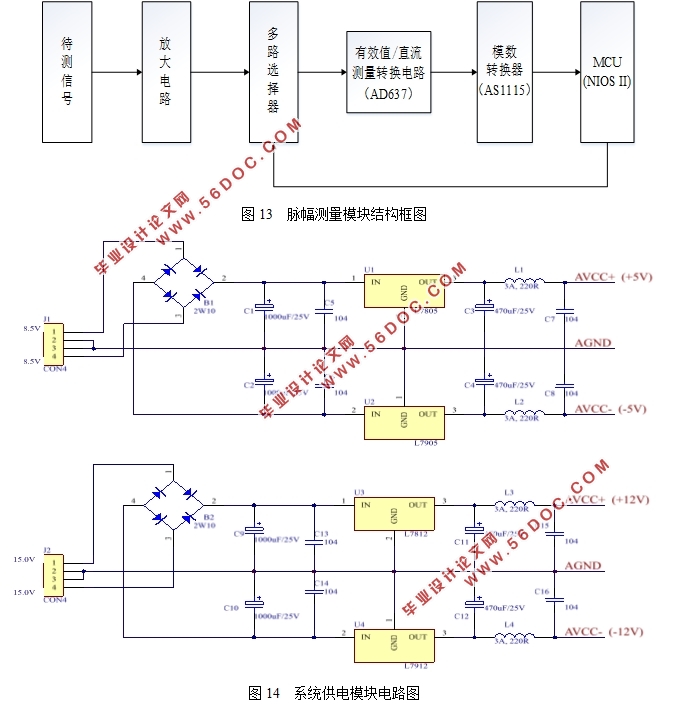

4.1系统供电模块设计 12

4.2增益控制模块设计 13

4.2.1模块整体结构框图 13

4.2.2 模块各子电路设计 14

4.3 高速比较电路模块设计 15

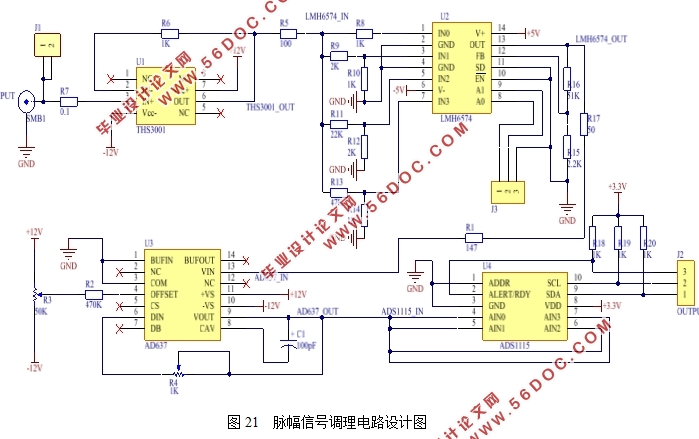

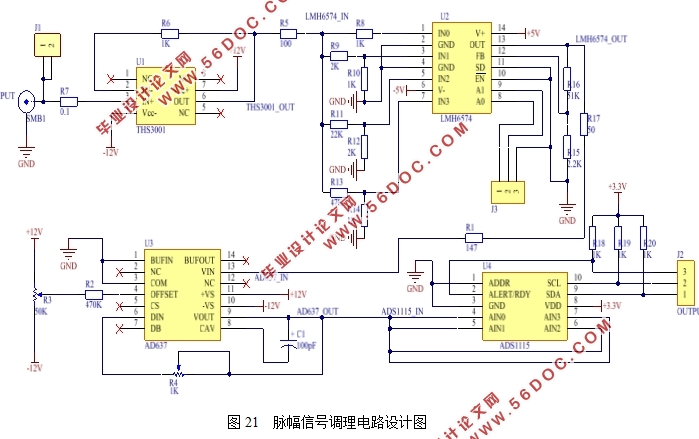

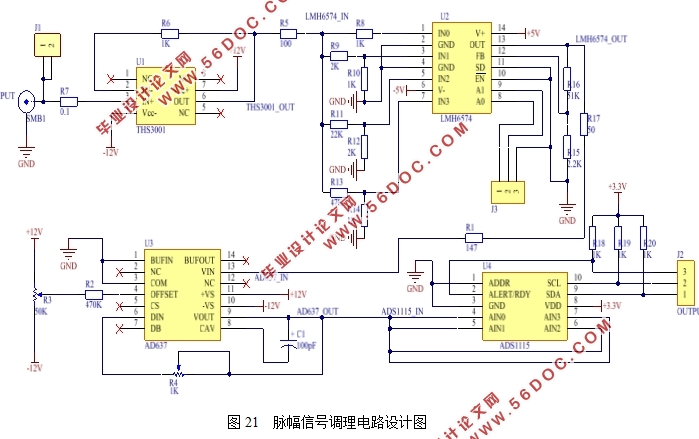

4.4脉幅调理模块设计 15

4.5 FPGA内部模块设计 16

4.5.1 FPGA系统顶层原理图 16

4.5.2模块计数器及锁相环设计 17

4.5.3 NiosII软核配置与搭建 20

4.5.4系统软核编程设计 22

4.6本章小结 24

5 系统调试及性能优化 24

5.1本系统中FPGA器件芯片 24

5.2系统调试及结果分析 25

5.3测量方法的优化 26

5.4本章小结 27

6 结论与展望 27

参考文献: 28

致谢 30

|