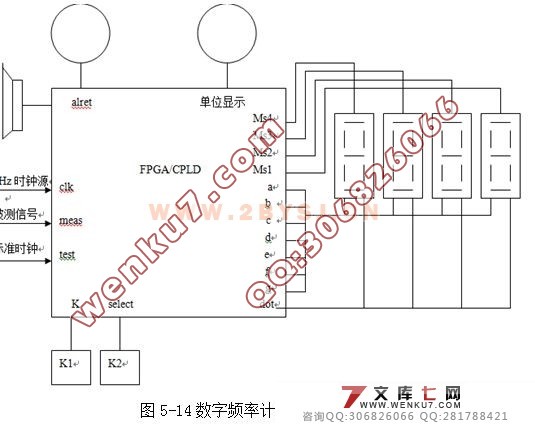

测量仪器-数字频率计的设计(Max+plusⅡ仿真)

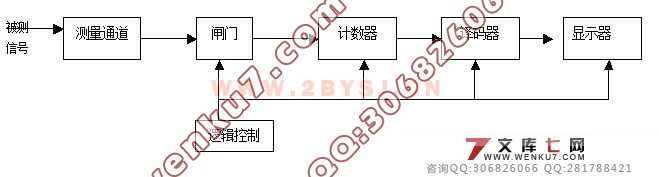

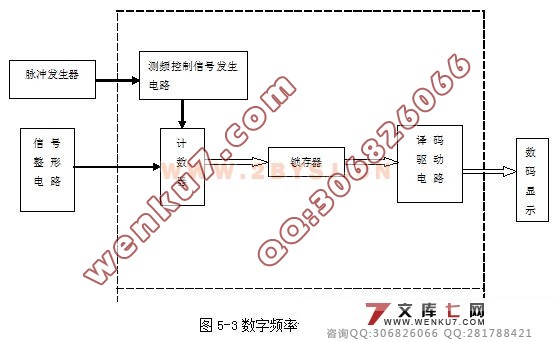

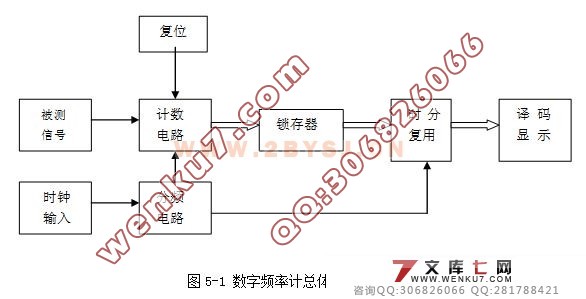

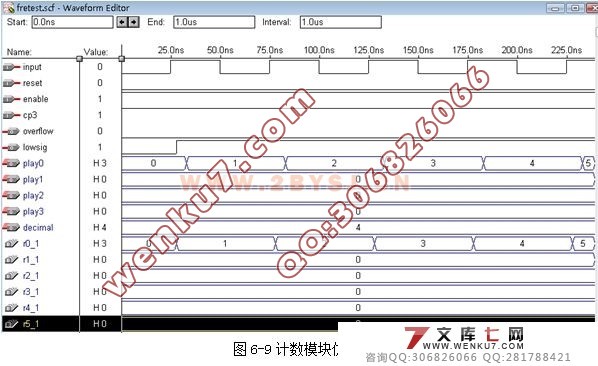

数字频率计是一种基本的测量仪器。它被广泛应用与航天、电子、测控等领域。它利用VHDL硬件描述语言进行设计,并在EDA(电子设计自动化)工具的帮助下,用大规模可编程器件(CPLD)实现数字频率计的设计原理及相关程序。通过了Max+plusⅡ软件进行仿真、硬件调试和软硬件综合测试特点是:无论底层还是顶层文件均用VHDL(硬件语言)语言编写,避免了用电路图设计时所引起的毛刺现象;改变了以往数字电路小规模多器件组合的设计方法。整个频率计设计在一块CPLD芯片上,与用其他方法做成的频率计相比,体积更小,性能更可靠。 频率计是数字电路中的典型器件,其实现的方法,选用的器件也是多种多样的。本次虽然也是频率计的设计,单采用了ISP技术。用CPLD来实现,是对典型电路的一个新型设计方法的尝试。这个设计过程无不体现:正是由于ISP技术的优越性,使整个系统从最初方案的设计到编写程序。从仿真调试到下载试验,都显得相当快捷和方便。采用ISP技术有简化生产流程且无引脚损伤,实现多功能硬件,为进行测试而重构逻辑等优点。另外,正是因ISP技术使硬件设计“软件化”了,对系统的维护和现场开发只是凭借一张磁盘就能实现,而这在常规逻辑技术下几乎是不可能的。随着网络技术的日益完善。通过网络来对远隔万里的用户系统进行软件版本升级换代,将给厂家与用户带来更多方便。 |