еЊ вЊ

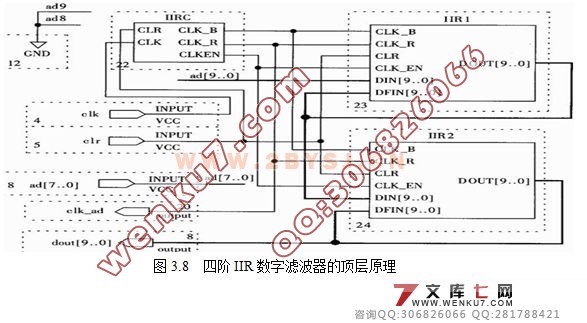

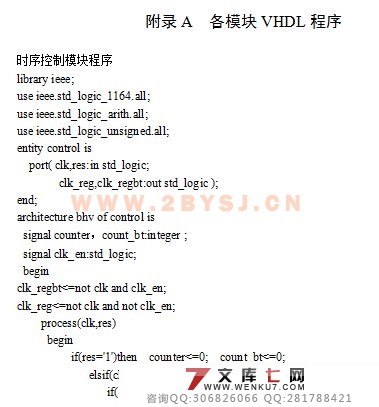

Ъ§зжаХКХДІРэдкПЦбЇКЭЙЄГЬММЪѕаэЖрСьгђжаЕУЕНЙуЗКЕФгІгУЃЌгыFIRЪ§зжТЫВЈЦїЯрБШЃЌIIRЪ§зжТЫВЈЦїПЩвдгУНЯЕЭЕФНзЪ§ЛёЕУНЯИпЕФбЁдёадЃЌЙЪБОПЮЬтВЩгУвЛжжЛљгкFPGAЕФIIRЪ§зжТЫВЈЦїЕФЩшМЦЗНАИ,ЪзЯШЗжЮіСЫIIRЪ§зжТЫВЈЦїЕФдРэМАЩшМЦЗНЗЈЃЌШЛКѓЭЈЙ§MAX+PLUSЂђЕФЩшМЦЦНЬЈЃЌВЩгУздЖЅЯђЯТЕФФЃПщЛЏЩшМЦЫМЯыНЋећИіIIRЪ§зжТЫВЈЦїЗжЮЊЃКЪБађПижЦЁЂбгЪБЁЂВЙТыГЫМгКЭРлМгЫФИіЙІФмФЃПщЁЃЗжБ№ЖдИїФЃПщВЩгУVHDLНјааУшЪіКѓЃЌНјааСЫЗТецКЭзлКЯЁЃЗТецНсЙћБэУїЃЌБОПЮЬтЫљЩшМЦЕФIIRЪ§зжТЫВЈЦїдЫЫуЫйЖШНЯПь,ЯЕЪ§ИФБфСщЛюЃЌгаНЯКУЕФВЮПММлжЕЁЃ

ЙиМќДЪЃКЕчзгЩшМЦздЖЏЛЏ; IIRЪ§зжТЫВЈЦї; ЯжГЁПЩБрГЬУХеѓСа; гВМўУшЪігябд

The design for IIR digital filter based on FPGA

Abstract

Digital signal processing is widely used in lots of fields, such as in science and project technique. Compared with FIR digital filter, IIR digital filter can get high selectivity with low factorial. A kind of IIR digital filter design method was introduced in the paper, which is based on FPGA. By used the design plant of MAX+PLUSЂђ, we adopt blocking method named ЁАTop-down ЁБ and divide the entire IIR digital filter into four blocks, which are Clock control, Time delay, Multiply-addition and Progression. After described with VHDL, we do emulate and synthesis to each block. The result shows that, the introduced IIR digital filter runs fast, and the coefficient changes agility. It has high worth for consulting.

Key WordsЃКElectronic Design Automation; IIR Digital Filter; Field Programmable Gate Array; very High Speed Integrated Circuit Hardware Description Language (VHDL)

IIRЪ§зжТЫВЈЦїИХФю

Ъ§зжТЫВЈЦїЪЧЭъГЩаХКХТЫВЈДІРэЙІФмЕФЃЌгУгаЯоОЋЖШЫуЗЈЪЕЯжЕФРыЩЂЪБМфЯпадЗЧЪББфЯЕЭГ[2]ЁЃЪфШывЛзщЪ§зжСПЃЌЭЈЙ§дЫЫуЪфГіЕФЪЧСэвЛзщЪ§зжСПЁЃЪ§зжТЫВЈЦїОпгаЮШЖЈадКУЁЂОЋЖШИпЁЂСщЛюадДѓЕШЭЛГігХЕуЁЃЫцзХЪ§зжММЪѕЕФЗЂеЙЃЌгУЪ§зжММЪѕЩшМЦТЫВЈЦїЕФЙІФмдНРДдНЪмЕНШЫУЧЕФзЂвтКЭЙуЗКЕФгІгУЁЃ

ФП ТМ 11000зж

еЊ вЊ I

Abstract II

в§ бд 1

1 IIRЪ§зжТЫВЈЦїМАЦфгВМўЪЕЯжЗНЗЈ 2

1.1 IIRЪ§зжТЫВЈЦїИХФю 2

1.1.1 IIRЪ§зжТЫВЈЦїЕФдРэ 2

1.1.2 IIRЪ§зжТЫВЈЦїЕФЛљБОНсЙЙ 2

1.1.3 IIRЪ§зжТЫВЈЦїЕФЩшМЦЗНЗЈ 3

1.2 IIRЪ§зжТЫВЈЦїЕФгВМўЪЕЯжЗНАИ 3

2 EDAММЪѕКЭПЩБрГЬТпМЦїМў 8

2.1 ЕчзгЩшМЦздЖЏЛЏEDAММЪѕ 8

2.2 ПЩБрГЬТпМЦїМў 8

2.2.1 ПЩБрГЬТпМЦїМўМђНщ 8

2.2.2 ЪЙгУFPGAЦїМўНјааПЊЗЂЕФгХЕу 9

2.2.3 FPGAЩшМЦЕФПЊЗЂСїГЬ 9

2.3 гВМўУшЪігябдVHDLМАЪ§зжЯЕЭГЩшМЦЗНЗЈ 10

2.3.1 гВМўУшЪігябдVHDLМђНщ 10

2.3.2РћгУVHDLЩшМЦЪ§зжЯЕЭГ 10

(БЯвЕЩшМЦ)

3 IIRЪ§зжТЫВЈЦїЕФЩшМЦгыЗТецНсЙћЗжЮі 11

3.1 ИїФЃПщЕФЩшМЦгыЗТецНсЙћЗжЮі 11

3.1.1 ЪБађПижЦФЃПщЕФЩшМЦгыЗТецНсЙћЗжЮі 11

3.1.2 бгЪБФЃПщЕФЩшМЦгыЗТецНсЙћЗжЮі 11

(БЯвЕЩшМЦ)

3.1.3 ВЙТыГЫМгФЃПщЕФЩшМЦгыЗТецНсЙћЗжЮі 12

3.1.4 РлМгФЃПщЕФЩшМЦгыЗТецНсЙћЗжЮі 13

3.1.5 ЖЅВуФЃПщЩшМЦ 14

3.2 IIRЪ§зжТЫВЈЦїЕФЗТецгыНсЙћЗжЮі 14

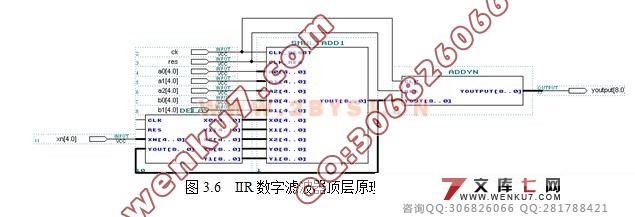

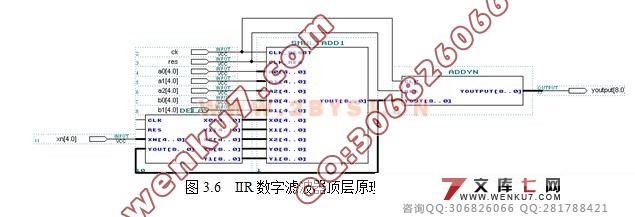

3.2.1 IIRЪ§зжТЫВЈЦїЕФЯЕЭГЩшМЦ 14

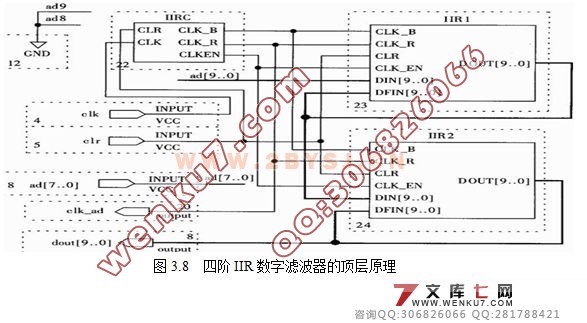

3.2.2 IIRЪ§зжТЫВЈЦїЕФЯЕЭГЗТецгыНсЙћЗжЮі 15

3.2.3 ИпНзIIRЪ§зжТЫВЈЦїЕФЪЕЯж 17

Нс Тл 19

ВЮ ПМ ЮФ Яз 20

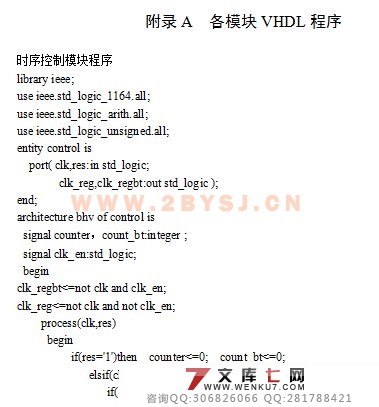

ИНТМA ИїФЃПщVHDLГЬађ 21

жТ аЛ 31 |