»щУЪFPGAәНMCUөДЛЕ·юөз»ъҝШЦЖЖчЙијЖ(ВЫОД)

АҙФҙЈәwenku7.com ЧКБПұаәЕЈәWK73469 ЧКБПөИј¶ЈәЎпЎпЎпЎпЎп %E8%B5%84%E6%96%99%E7%BC%96%E5%8F%B7%EF%BC%9AWK73469

ТФПВКЗЧКБПҪйЙЬ,ИзРиТӘНкХыөДЗлідЦөПВФШЎЈ

1.ОЮРиЧўІбөЗВј,Ц§ё¶әу°ҙХХМбКҫІЩЧчјҙҝЙ»сИЎёГЧКБП.

2.ЧКБПТФНшТіҪйЙЬөДОӘЧј,ПВФШәуІ»»бУРЛ®УЎ.ЧКБПҪц№©С§П°ІОҝјЦ®УГ. ГЬ ұЈ »Э °пЦъ

ЧКБПҪйЙЬ

ХӘ ТӘ

ұҫОДКЧПИ¶ФНЁУГЛЕ·юҝШЦЖЖҪМЁПоДҝЧцБЛХыМеөДЙијЖ№ж»®Ј¬ІўЧЕЦШ·ЦОцБЛ»щУЪFPGAөДөз»ъҪУҝЪДЈҝйөДЙијЖәНәЛРДЛг·ЁЈ¬ёшіцПаУҰөДҪУҝЪөзВ·Ј¬Іў¶ФөИҫ«¶ИЛг·ЁәНЙијЖЛјВ·ФЪALTERA QUARTUS 9.0өД»·ҫіПВҪшРРБЛ·ВХжЈ¬ФЪКөСйөзВ·ЙПҪшРРБЛІвКФЎЈЦчТӘДҝөДФЪУЪСРҫҝіцТ»ҝоёЯРФДЬөД»щУЪFPGAөДЛЕ·юөз»ъҪУҝЪДЈҝйЎЈ

№ШјьҙКЈәЛЕ·юҝШЦЖЖҪМЁ FPGA өИҫ«¶ИЛг·Ё өз»ъҪУҝЪДЈҝй

THE DESIGN OF FPGA+MCU BASED SERVO

MOTOR CONTROLLER

ABSTRACT

This first general-purpose of this dissertation is the overall project design and planning for the servo control platform, and also it analyzed the core algorithms for the FPGA based interface design. Given a appropriate interface circuit ,An equal precision algorithms designed with FPGA is introducedЈ®It adopts Verilog Hardware

Description Language to implement in servo motor interface modules ,and adds pulse width measurement on the base of traditional frequency measurement, and the HDL was simulated in the ALTERA QUARTUS 9.0 environment. Intended to design a high-performance FPGA-based servo motor interface module.

KeywordsЈәservo control platform FPGA equal precision algorithm servo motor interface module

ЛЕ·юөз»ъјтҪй

Т»ёцЛЕ·юөз»ъДЪІҝТ»°г°ьАЁТ»ёцЦұБчөз»ъЎўТ»ЧйұдЛЩіЭВЦЧйЎўТ»ёц·ҙАЎҝЙөчөзО»ЖчТФј°Т»ҝйөзЧУҝШЦЖ°еЎЈЖдЦРЈ¬ёЯЛЩЧӘ¶ҜөДөз»ъМṩБЛФӯКј¶ҜБҰЈ¬ҙш¶ҜұдЛЩЈЁјхЛЩЈ©іЭВЦЧйЈ¬К№Ц®ІъЙъёЯЕӨБҰөДКдіцЎЈіЭВЦЧйөДұдЛЩұИФҪҙуЈ¬ЛЕ·юөз»ъөДКдіцЕӨБҰТІФҪҙуЈ¬ТІҫНКЗЛөФҪДЬіРКЬёьёЯөДёәФШЈ¬ө«ЧӘ¶ҜөДЛЩ¶ИТІПаУҰФҪөНЎЈ

ЛЕ·юөз»ъ№ӨЧчФӯАн

ЛЕ·юөз»ъКЗТ»ёцөдРНұХ»··ҙАЎПөНіЈ¬јхЛЩіЭВЦЧйУЙөз»ъЗэ¶ҜЈ¬ЖдЦХ¶ЛЈЁКдіц¶ЛЈ©ҙш¶ҜТ»ёцПЯРФөДұИАэөзО»ЖчЧчО»ЦГјмІвЈ¬ёГөзО»Жч°СЧӘҪЗЧшұкЧӘ»»ОӘТ»ұИАэөзС№·ҙАЎёшҝШЦЖПЯВ·°еЈ¬ҝШЦЖПЯВ·°еҪ«ЖдУлКдИлөДҝШЦЖВціеРЕәЕұИҪПЈ¬ІъЙъҫАХэВціеЈ¬ІўЗэ¶Ҝөз»ъХэПт»т·ҙПтөШЧӘ¶ҜЈ¬К№іЭВЦЧйөДКдіцО»ЦГУлЖЪНыЦөПа·ыЈ¬БоҫАХэВціеЗчУЪОӘ0Ј¬ҙУ¶шҙпөҪК№ЛЕ·юөз»ъҫ«И·¶ЁО»өДДҝөДЎЈ

Дҝ Вј 12000ЧЦ

ХӘТӘ

ABSTRACT

1ТэСФ ……………………………………………………………………1

1.1ПоДҝұіҫ° ……………………………………………………………1

1.2СРҫҝТвТе ……………………………………………………………1

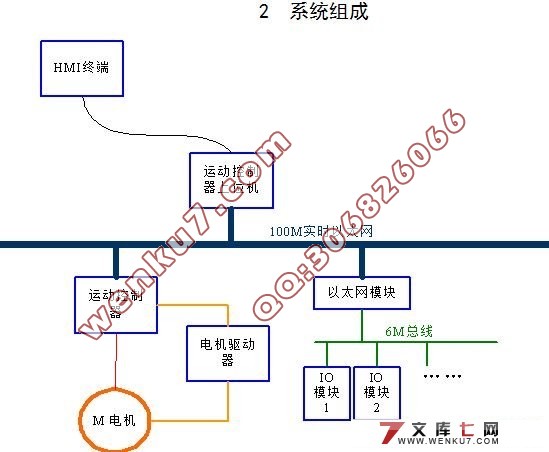

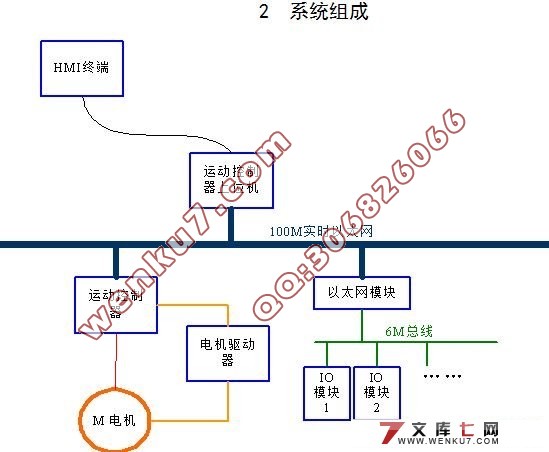

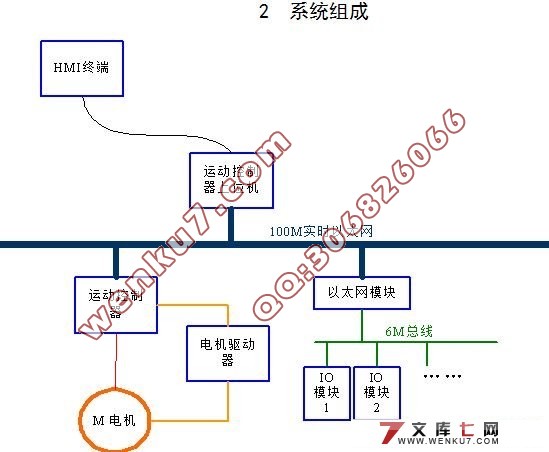

2 ПөНіЧйіЙ………………………………………………………………2

2.1 ФЛ¶ҜҝШЦЖЖч …………………………………………………………2

2.1.1 MCU№ҰДЬ …………………………………………………………2

2.1.2 FPGA№ҰДЬ …………………………………………………………2

2.1.3№вөзёфАлДЈҝй№ҰДЬ ………………………………………………2

2.2ЛЕ·юЗэ¶ҜЖч …………………………………………………………2

2.2.1іЈУГЛЕ·юЗэ¶ҜЖчјтҪй ………………………………………………2

2.3ЛЕ·юөз»ъ………………………………………………………………3

2.3.1ЛЕ·юөз»ъјтҪй………………………………………………………3

2.3.2ЛЕ·юөз»ъ№ӨЧчФӯАн…………………………………………………4

2.3.3ЛЕ·юөз»ъөДҝШЦЖ……………………………………………………4

2.4HMI ……………………………………………………………………4

2.5ҝШЦЖЖчЙПО»»ъІҝ·Ц……………………………………………………4

2.5.1ЙПО»»ъ№ҰДЬ…………………………………………………………4

2.6ТФМ«НшДЈҝй……………………………………………………………4

2.6.1ТФМ«НшДЈҝй№ҰДЬ……………………………………………………4

3 FPGAҪУҝЪДЈҝйПкПёҪйЙЬ………………………………………………5

3.1КөПЦ№ҰДЬ………………………………………………………………5

3.1.1 ЛЩ¶ИҝШЦЖДЈҝй ……………………………………………………5

3.1.2 О»ЦГҝШЦЖДЈҝй ……………………………………………………5

3.1.3 CPUҪУҝЪДЈҝй …………………………………………………………6

3.2ЛЩ¶ИУлО»ЦГјмІвЛг·ЁМЦВЫ………………………………………………6

3.2.1M·Ё……………………………………………………………………6

3.2.2T·Ё…………………………………………………………………6

3.2.3өИҫ«¶ИІвЖөЛг·Ё……………………………………………………6

3.2.4ёЯҫ«¶ИКэЧЦІвЛЩЛг·Ё………………………………………………9

3.3ЛЩ¶ИУлО»ЦГҝШЦЖЛг·Ё…………………………………………………20

3.4УІјюІҝ·Ц…………………………………………………………………14

3.4.1ALTERA FPGAҪйЙЬ ……………………………………………………14

3.4.2FPGAУІјюІҝ·Ц ………………………………………………………14

3.4.2.1өзФҙј°ҫ§ХсІҝ·Ц …………………………………………………14

3.4.2.2ДЪҙжј°FLASH ……………………………………………………15

3.4.2.3ЦчРҫЖ¬……………………………………………………………15

3.4.2.4JTAGПВФШ…………………………………………………………16

3.4.3КдИлКдіц№вөзёфАл…………………………………………………17

3.4.3.1КдИл№вөзёфАлДЈҝй………………………………………………17

3.4.3.2Кдіц№вөзёфАлДЈҝй………………………………………………18

3.5ИнјюІҝ·Ц ………………………………………………………………18

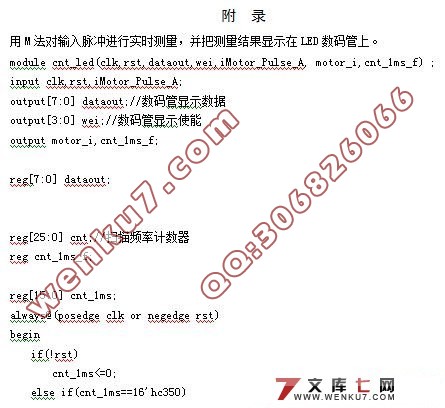

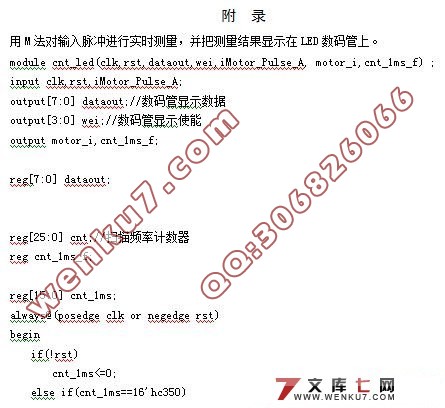

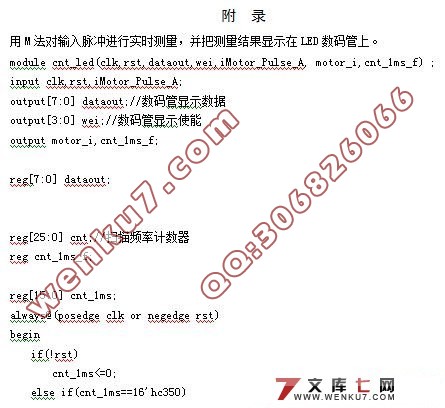

3.5.1 verilog HDLұаіМУпСФҪйЙЬ ………………………………………18

3.5.2КдИлКдіц¶ЛЧУ¶ЁТе……………………………………………………18

3.5.3јДҙжЖч¶ЁТе…………………………………………………………19

3.5.4FPGAјЬ№№………………………………………………………………20

3.5.5ЦчТӘДЈҝйҪйЙЬ ……………………………………………………20

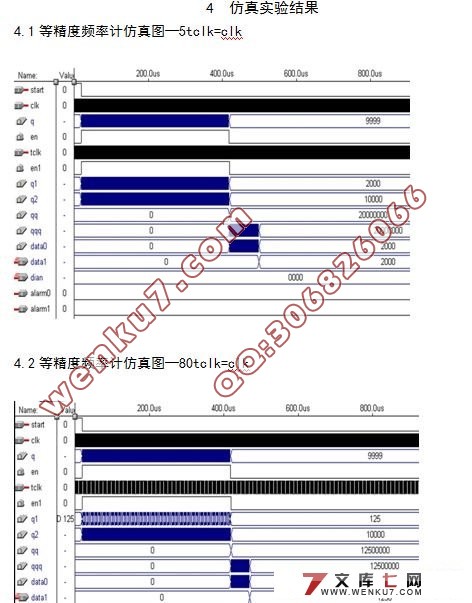

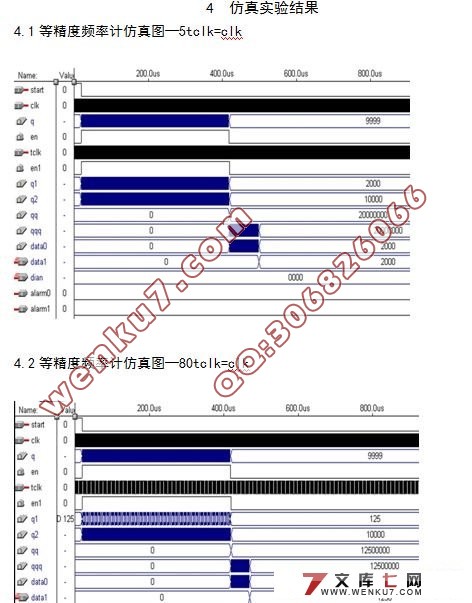

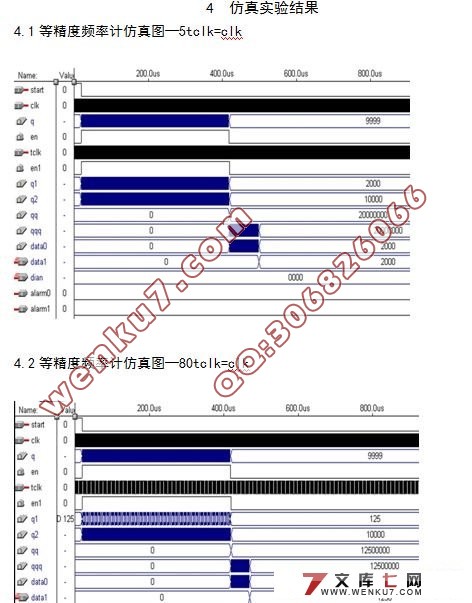

4 ·ВХжКөСйҪб№ы ……………………………………………………………22

5 УҰУГ°ёАэ …………………………………………………………………24

6 ҪбВЫ ………………………………………………………………………26

Р»ҙЗ

ІОҝјОДПЧ

ёҪВј

|