基于FPGA的信号源设计(论文14000字)

摘要:本文首先介绍了信号源的研究背景和DDS技术的理论,然后根据本课题目标和内容,结合 DDS技术,借助高集成度的 FPGA芯片,依靠 Quartus II和 Nios II集成开发环境平台,使用 verilog硬件描述语言和 C语言程序编程,实现一款高精度、低成本、多功能、便携式、高性价比的信号发生器。论文详细阐述了在QuartusⅡ环境中利用Verilog HDL语言设计信号发生器的过程,实现波形切换、任意频率和幅度可调的功能,并给出了相应的测试结果。实验结果表明,利用FPGA实现DDS技术从而制造出信号源的方案是切实可行,具有体型小、成本低、精度高等优点,是信号发生器未来的发展方向。

关键词:信号源;FPGA;DDS技术;verilog语言

Design and Implementation of Signal Source Based on FPGA

Abstract:This paper first introduces the research background of the signal source and the theory of DDS technology. Then, according to the goal and content of this project, combined with DDS technology, with highly integrated FPGA chip, relying on Quartus II and Nios II integrated development environment platform, using verilog hardware description Language and C language programming, to achieve a high-precision, low-cost, multi-functional, portable, cost-effective signal generator. In this paper, the process of designing the signal generator in Verilog HDL language in Quartus Ⅱ environment is described in detail, and the function of waveform switching, arbitrary frequency and amplitude is realized, and the corresponding test results are given. The experimental results show that it is feasible and feasible to implement DDS technology to realize the signal source by using FPGA. It has the advantages of small size, low cost and high precision, and is the future development direction of signal generator.

Key words:Signal source;FPGA;DDS technology;Verilog language

目 录

1、绪论 1

1.1、课题背景 1

1.2、信号发生器的功能 1

1.3、国内外信号源的发展现状 2

1.4、信号源的发展趋势及研究意义 3

1.5、课题研究内容及目标 4

2、 DDS信号发生器理论分析 5

2.1、频率合成技术简介 5

2.2、DDS基本原理和结构特点 5

2.2.1、DDS基本结构 5

2.2.2、DDS基本原理 7

2.2.3、DDS工作特点 8

2.3、DDS任意波形的产生 9

2.4、DDS技术的工作指标 10

3、 基于FPGA的DDS系统实现 11

3.1、FPGA简介 11

3.2、FPGA开发环境简介 11

3.3、信号发生器的FPGA实现 12

3.3.1、设计模块划分 13

3.3.2、时钟模块的设计 13

3.3.3、相位累加器模块的设计 14

3.3.4、波形存储器模块的设计 15

3.3.5、波形选择模块的设计 18

3.3.6、DA转换模块 19

3.4、芯片引脚定义 20

3.5、设计结果报告 20

4、 系统性能测试与误差分析 22

4.1、硬件调试 22

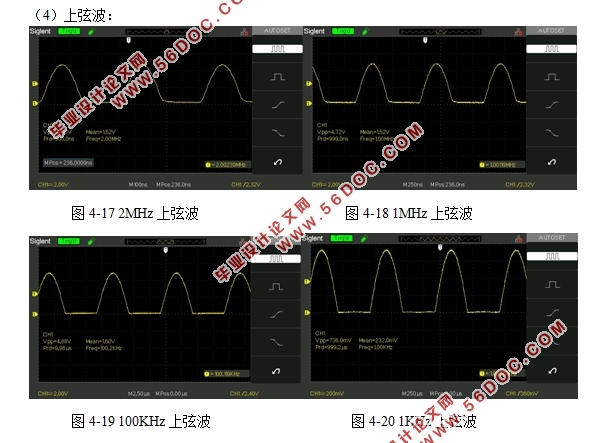

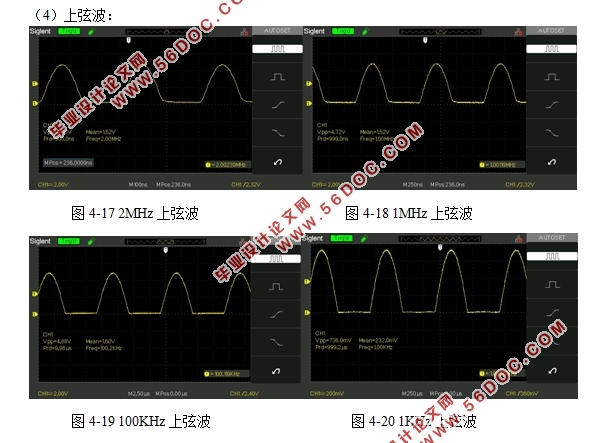

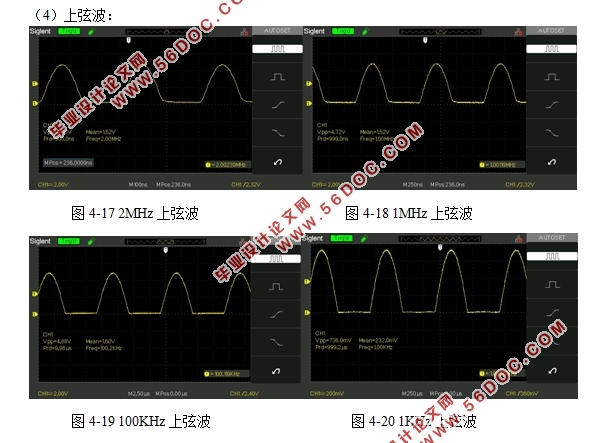

4.2、输出波形 22

4.3、性能指标 24

4.4、实物展示 25

5、总结与展望 27

参考文献 28

致谢 29

|