由单片机构成的锁相环实验平台软件设计

来源:wenku7.com 资料编号:WK73590 资料等级:★★★★★ %E8%B5%84%E6%96%99%E7%BC%96%E5%8F%B7%EF%BC%9AWK73590

以下是资料介绍,如需要完整的请充值下载。

1.无需注册登录,支付后按照提示操作即可获取该资料.

2.资料以网页介绍的为准,下载后不会有水印.资料仅供学习参考之用. 密 保 惠 帮助

资料介绍

由单片机构成的锁相环实验平台软件设计(含任务书,开题报告,外文翻译,答辩稿,毕业论文16000字)

摘要:锁相技术实验是通信工程本科专业的一门专业任选课程的配套实验,使学生可以系统地,全面地了解锁相环工作过程.对锁相环有感性认识掌握VCO压控振荡器的基本工作原理。它能加深学生对基本锁相环工作原理的理解,熟悉锁相式数字频率合成器的电路组成与工作原理。培养学生综合分析问题的能力,培养学生的实际动手能力,为学生今后从事通信相关的工作打下扎实基础。

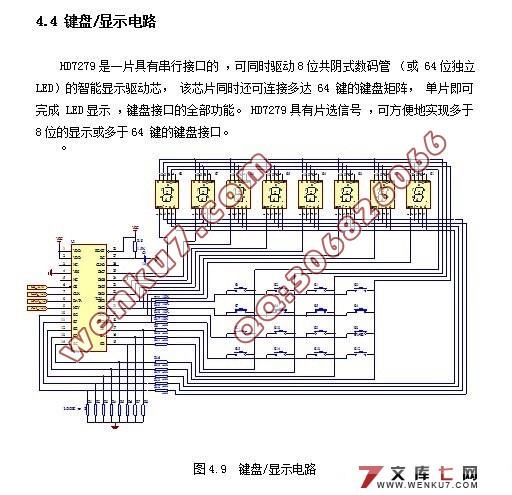

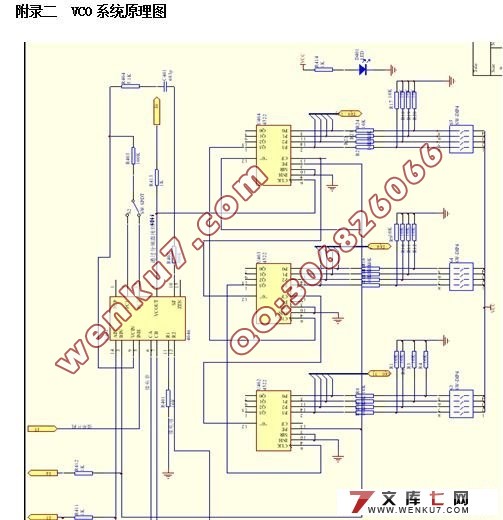

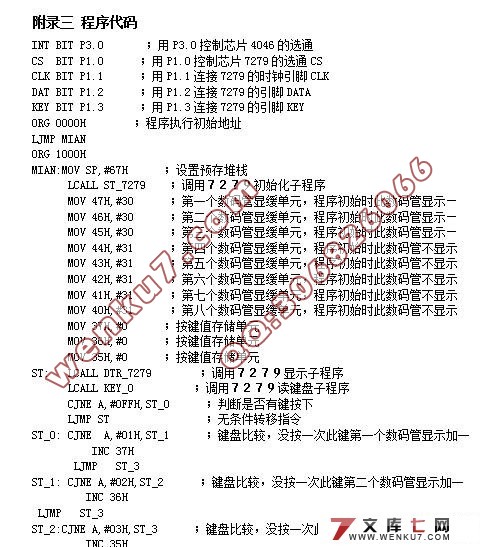

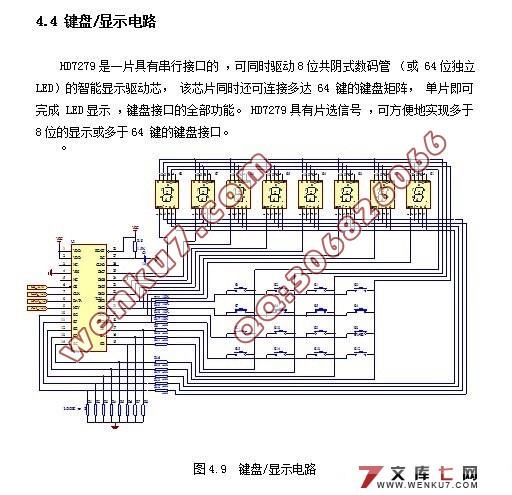

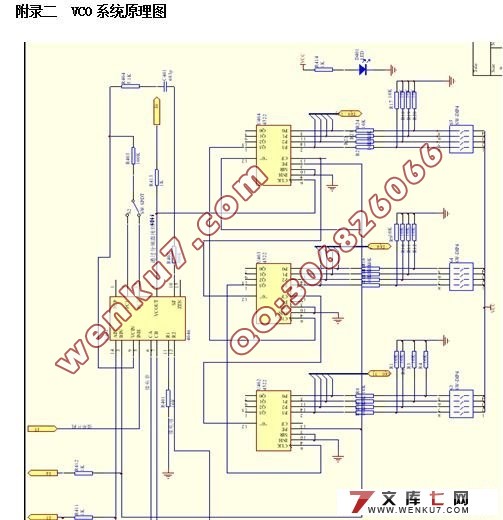

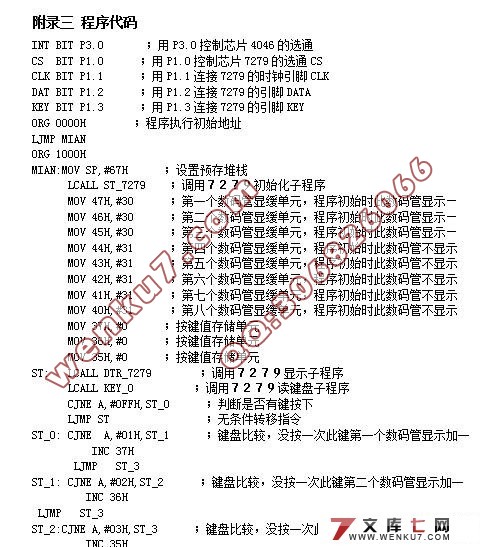

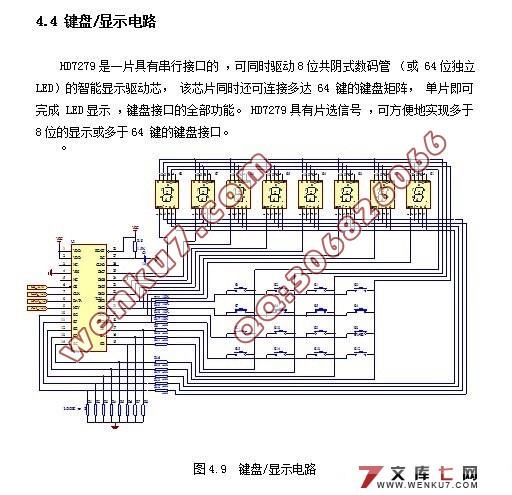

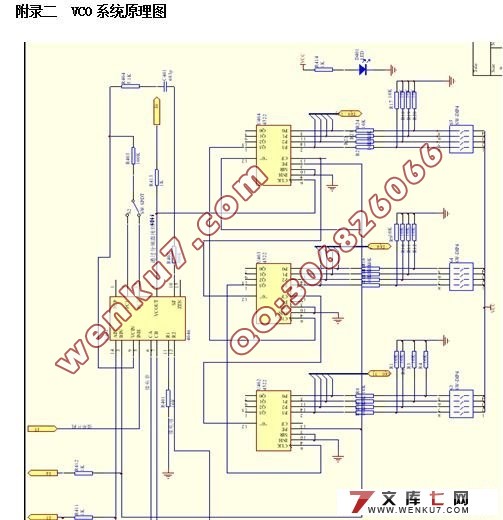

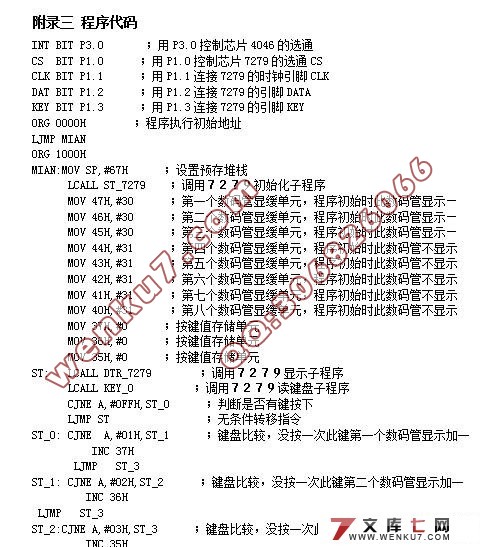

本文介绍采用单片机最小系统来控制锁相环系统的分频比,要求能通过键盘和LED数码管来输入显示分频比。键盘和显示部分采用HD7279芯片来控制实现。锁相环部分则采用CD4046和4522芯片,本文对这部分有详细的介绍。程序设计使用汇编语言来实现,通过Keil C软件来编译,本文介绍了程序设计的思路及流程,着重介绍了程序的编写过程。

关键词:锁相环 分频比 HD7279 CD4046 汇编语言

The software design of the PLL experimental platform based on MCU

Abstract: Phase-locked technology experiment is a communication engineering undergraduate professional profession optional course of supporting experiment, so that the students can systematically and comprehensively understand the working process of phase-locked loop. Have the perceptual knowledge of the PLL(Phase Lock Loop) and understand the VCO(Voltage Contraller Oscillator) basic grase work .It can ehance the students understanding the basic principle of phase-locked loop,PLL familiar with digital frequency synthesizer circuit and working principle. This paper can train comprehensive analysis of students and develop students practical ability for students to engage in communications-related work in the future .

The artical introduces to use the MCU’s minimum system to control the PLL divider system, through the keyboard and asked to enter the LED digital display divider. The keyboard and display part adopts HD7279 chip to control realization.PLL part is constituted by CD4046 and 4522 chips and the paper describes in detail in this section. Programming in assembly language to achieve, through Keil C compiler software, this paper introduces the idea of program design and processes, focusing on the preparation of the program.

Keywords: PLL diver HD7279 CD4046 assembly language

1.3 本课题主要研究内容

研制一个由单片机和锁相环组成的频率合成器,通过实验设备能观察锁相环的同步过程、跟踪过程、捕捉过程,测量锁相环的同步带与捕捉带,并计算它们的带宽。能测量输入和输出信号的波形,测量并观察最小分频比和最大分频比,并能通过单片机程序设计方法来控制锁相环分频比,用键盘来输入,数码管来显示。

2 锁相环实验平台系统设计

2.1 系统设计要求及技术指标

本系统采用单片机STC89C52、VOC压控振荡器,相位比较器,环路滤波器为核心器件来进行锁相环的实验平台的设计。实现具有键盘输入和显示功能,输出频率f0=1.000~999KHZ, 频率间隔1KHZ。输出电平:TTL电平,电源:+5V。

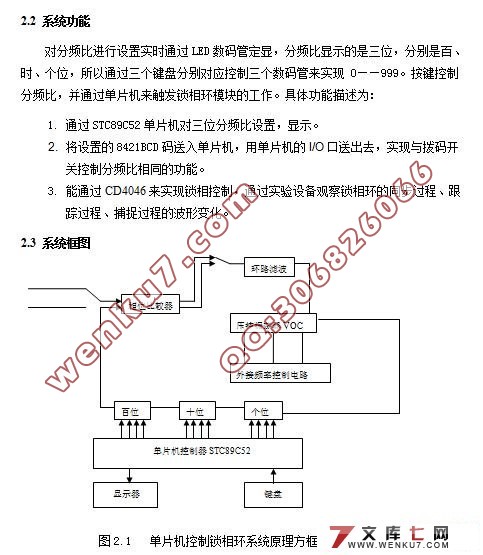

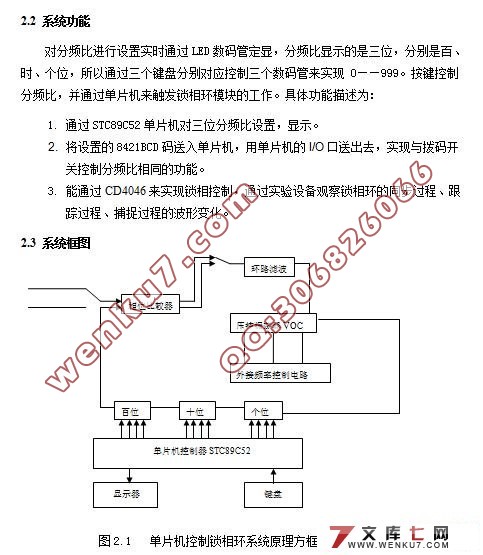

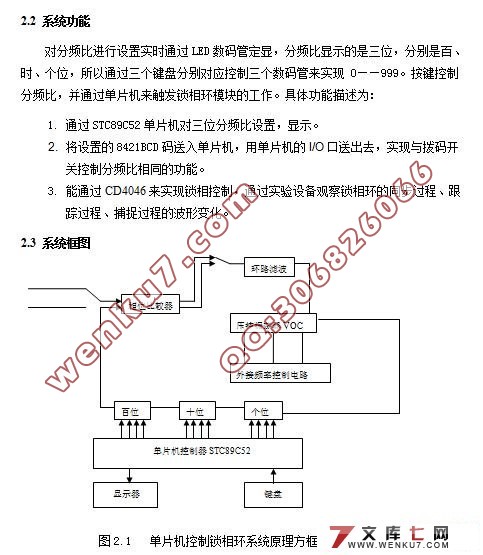

2.2 系统功能

对分频比进行设置实时通过LED数码管定显,分频比显示的是三位,分别是百、时、个位,所以通过三个键盘分别对应控制三个数码管来实现0——999。按键控制分频比,并通过单片机来触发锁相环模块的工作。具体功能描述为:

1. 通过STC89C52单片机对三位分频比设置,显示。

2. 将设置的8421BCD码送入单片机,用单片机的I/O口送出去,实现与拨码开关控制分频比相同的功能。

3. 能通过CD4046来实现锁相控制,通过实验设备观察锁相环的同步过程、跟踪过程、捕捉过程的波形变化。

目 录

1 前言

1.1课题的背景及意义 1

1.2国内外研究概况及发展趋势 2

1.3本课题主要研究内容 4

2 锁相环实验平台系统设计

2.1 系统设计要求及技术指标 5

2.2 系统思路及功能 5

2.3 系统框图 5

3 由锁相环构成的频率合成器基本工作原理

3.1 锁相环的工作原理 7

3.2 频率合成器的工作原理 8

4 单片机构成的锁相环实验平台硬件设计

4.1 单片机最小系统电路 9

4.2 锁相环电路 10

4.3 分频比控制电路 11

4.4 键盘/显示电路 12

5 单片机构成的锁相环实验平台软件设计

5.1 软件设计总体思路及流程图 13

5.2 编程语言的选择 15

5.3 各子程序模块设计 16

5.3.1 HD7279芯片的编程介绍 16

5.3.2 显示子程序模块 22

5.3.3 键扫子程序模块 23

5.3.4 功能键模块 24

5.3.5 数值键模块 24

5.3.4 单片机向HD7279发送指令及数值子程序 25

5.3.5 单片机从HD7279接收指令及键盘值子程序 26

6 系统调试

6.1 系统软件调试 27

6.2 软硬件联合调试 28

6.3 实验调试 28

7 结论 30

参考文献 31

致谢 32

附录 33

|